### ANALOG GENERATOR FOR A DRIVER OF A BOOST DC-DC CONVERTER

## A THESIS SUBMITTED TO THE FACULTY OF ARCHITECTURE AND ENGINEERING OF EPOKA UNIVERSITY

BY

ANDI GJINI

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN ELECTRONICS AND COMMUNICATION ENGINEERING

NOVEMBER, 2024

#### Approval sheet of the Thesis

This is to certify that we have read this thesis entitled "Analog Generator for a driver of a boost DC-DC converter" and that in our opinion it is fully adequate, in scope and quality, as a thesis for the degree of Master of Science.

> Assoc. Prof. Dr. Arban Uka Head of Department Date: November, 21, 2024

Examining Committee Members:

| Prof. Dr. Gëzim Karapici | (Computer Engineering) |

|--------------------------|------------------------|

| Dr. Florenc Skuka        | (Computer Engineering) |

| Dr. Shkëlqim Hajrulla    | (Computer Engineering) |

I hereby declare that all information in this document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Name Surname: Andi Gjini

Signature: \_\_\_\_\_

### ABSTRACT

### ANALOG GENERATOR FOR A DRIVER OF A BOOST DC-DC CONVERTER

Gjini, Andi M.Sc., Department of Computer Engineering Supervisor: Prof. Dr. Gëzim Karapici

This thesis explores the automation of analog circuit design, focusing on the driver of a boost DC-DC converter. It develops methodologies for automating schematic and layout design using tools like ANAGEN, WiCked, and Qgen. By transitioning from traditional manual methods to reusable, parameterized analog generators, the proposed approach significantly reduces design time and enhances scalability. The implementation demonstrates the effectiveness of automated optimization and layout strategies in meeting stringent design requirements, offering a practical solution for advancing analog design automation.

Keywords: Anagen, WiCked, Qgen, Python, Schematic Generator, Layout Generator

### ABSTRAKT

### GJENERATOR ANALOG PER NJE DREJTUES TE NJE KONVERTERI NXITES DC-DC

#### Gjini, Andi

Master Shkencor, Departamenti i Inxhinierisë Kompjuterike

Udhëheqësi: Prof. Dr. Gëzim Karapici

Kjo tezë eksploron automatizimin e dizajnit të qarkut analog, duke u fokusuar në drejtuesin e një konverteri nxitës DC-DC. Ai zhvillon metodologji për automatizimin e dizajnit skematik dhe të paraqitjes duke përdorur mjete si ANAGEN, WiCked dhe Qgen. Duke kaluar nga metodat tradicionale manuale te gjeneratorët analogë të ripërdorshëm, të parametrizuar, qasja e propozuar redukton ndjeshëm kohën e projektimit dhe rrit shkallëzueshmërinë. Zbatimi demonstron efektivitetin e optimizimit të automatizuar dhe strategjive të paraqitjes në përmbushjen e kërkesave të rrepta të projektimit, duke ofruar një zgjidhje praktike për avancimin e automatizimit të dizajnit analog.

Fjalët kyçe: Anagen, WiCked, Python, Schematic Generator, Layout Generator

## **ACKNOWLEDGEMENTS**

Thanks to my professor, colleagues and whoever supported me.

## **TABLE OF CONTENTS**

| ABSTRACT iii                     |

|----------------------------------|

| ABSTRAKTiv                       |

| ACKNOWLEDGEMENTSv                |

| LIST OF TABLES viii              |

| INTRODUCTION1                    |

| 1.1 ANAGEN5                      |

| 1.2 WiCked                       |

| 1.3 Qgen                         |

| 1.3.1 Layout generator structure |

| SCHEMATIC GENERATOR              |

| 2.1 Test case presentation       |

| 2.2 Driver                       |

| 2.2.1 Methodoloy                 |

| LAYOUT GENERATOR45               |

| 3.1 Analog layout strategies     |

| 3.2 Driver Layout template       |

| 3.3 Qgen: Layout creation        |

| RESULTS                          |

| 4.1 Schematic Generator flow     |

| 4.1.1 Pre-Layout Verification    |

| 4.2 W  | iCked Optimisation       | 70 |

|--------|--------------------------|----|

| 4.2.1  | Wicked Flow              | 81 |

| 4.2.2  | Verification Result      | 89 |

| 4.3 La | ayout generator: Driver  | 91 |

| 4.3.1  | Post-layout verification | 92 |

| CONCL  | USION                    | 94 |

## LIST OF TABLES

| Table 4.1 Specifications in typical conditions        |

|-------------------------------------------------------|

| Table 4.2. Tables for measurements specifications     |

| Table 4.3. Tables for timing performances improvement |

# List of Figures

| Figure 1: Estimated hardware design                    | .2 |

|--------------------------------------------------------|----|

| Figure 2: ANAGEN                                       | 5  |

| Figure 3: Anagen Framework                             | 8  |

| Figure 4: ANAGEN Framework simplified                  | 9  |

| Figure 5: Anagen Workflow                              | 10 |

| Figure 6: WiCked Tasks                                 | 15 |

| Figure 7: Constraint Editor                            | 15 |

| Figure 8: WiCked GUI                                   | 16 |

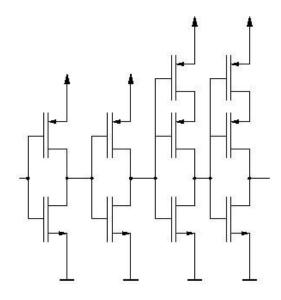

| Figure 9: Qgen transistor matrix                       | 18 |

| Figure 10: Qgen transistor matrix GUI                  | 18 |

| Figure 11: Qgen project structure                      | 19 |

| Figure 12: Test case presantation                      | 22 |

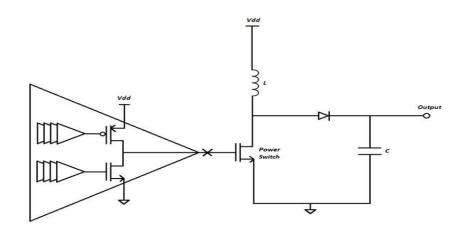

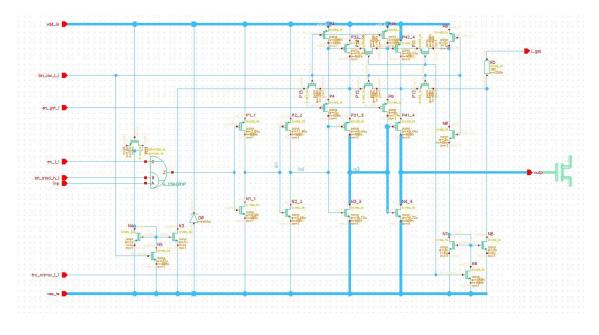

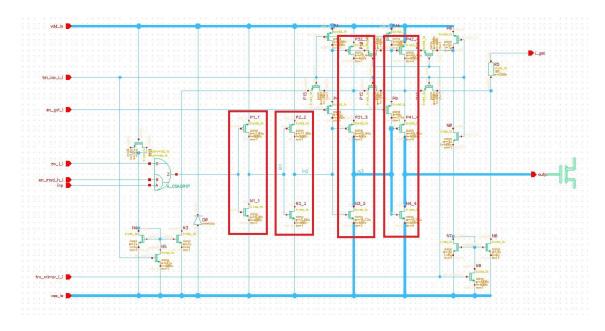

| Figure 13: Internal driver structure                   | 23 |

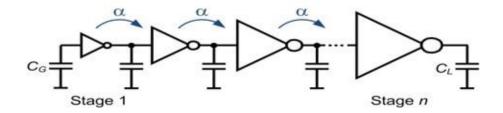

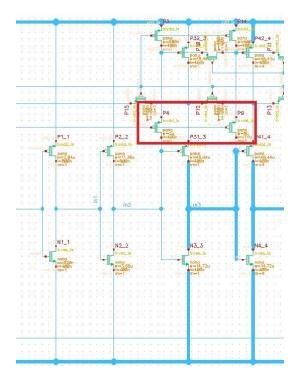

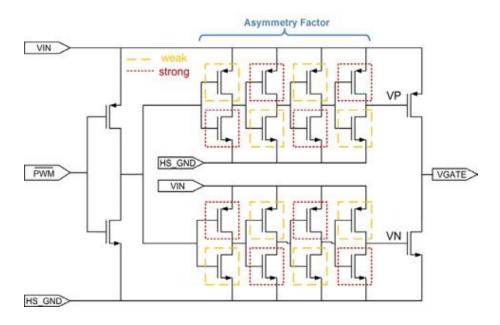

| Figure 14: Driver topology                             | 24 |

| Figure 15: Driver topology with the stages highlighted | 25 |

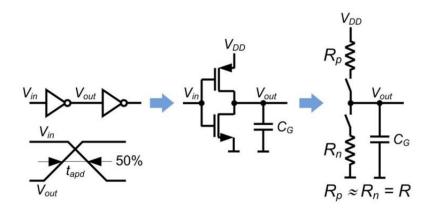

| Figure 16: Inverter single stage                       | 27 |

| Figure 17: Driver stages                               | 28 |

| Figure 18: Pmoses as switches                          | 29 |

| Figure 19: Simplified version                               |

|-------------------------------------------------------------|

| Figure 20: Asymmetrical sizing                              |

| Figure 21: First stage dimension                            |

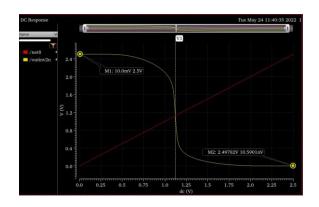

| Figure 22: First stage characteristic                       |

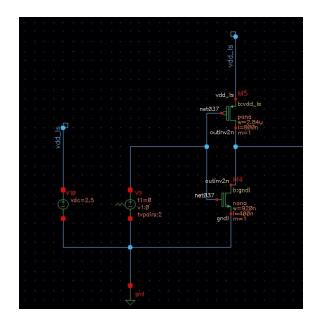

| Figure 23: Input capacitance measure                        |

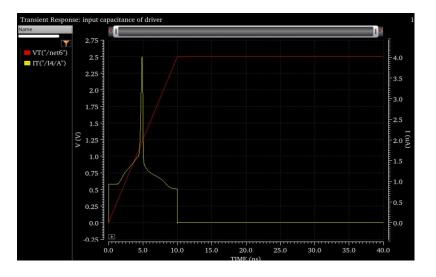

| Figure 24: Input current absorbed                           |

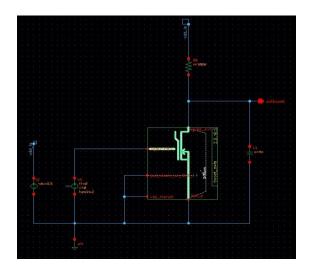

| Figure 25: Configuration for output capacitance calculation |

| Figure 26: Output current absorbed                          |

| Figure 27: Workflow                                         |

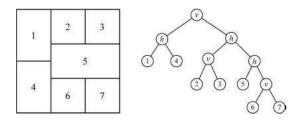

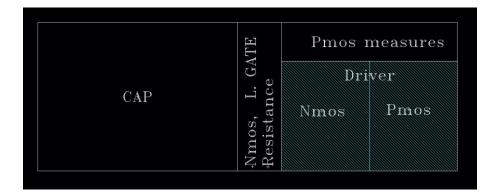

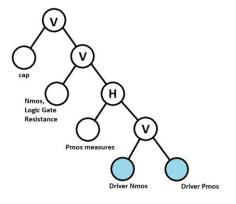

| Figure 28: Slicing floorplan template and binary tree46     |

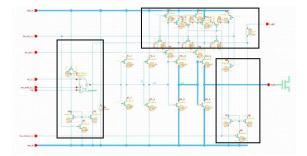

| Figure 29: Circuitry around the Driver47                    |

| Figure 30: Template                                         |

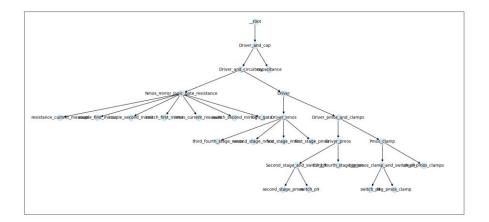

| Figure 31: Binary tree description of the template          |

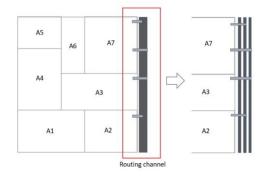

| Figure 32: Routing channel example49                        |

| Figure 33: Modules implemented by Qgen50                    |

| Figure 34: Tree description51                               |

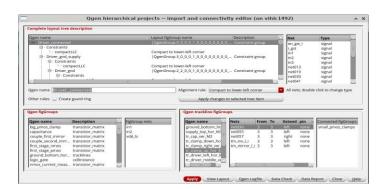

| Figure 35: Import and connectivity editor                   |

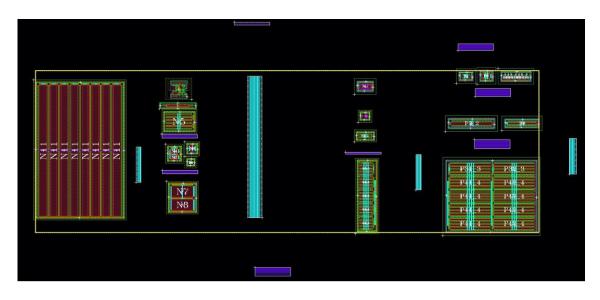

| Figure 36: Template with modules and tracks                 |

| Figure 37: Hierarchical tree description                    |

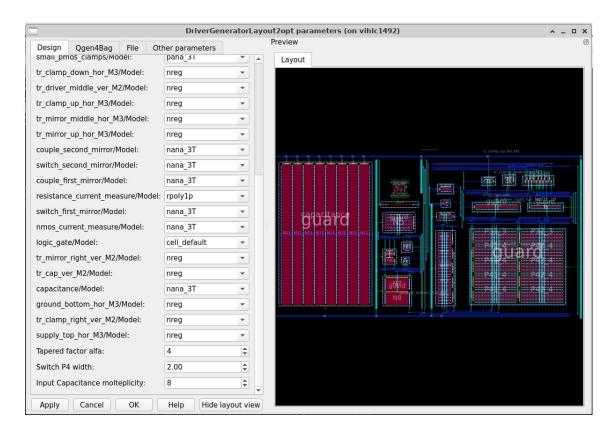

| Figure 38: Driver generator GUI                                      | 54 |

|----------------------------------------------------------------------|----|

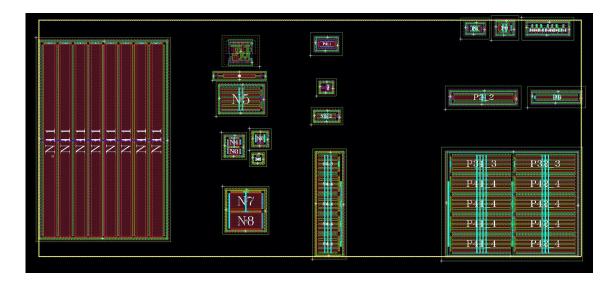

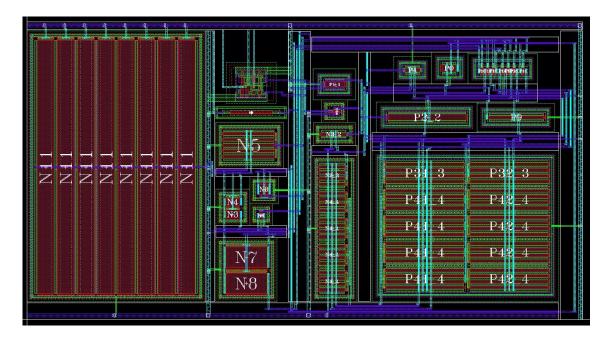

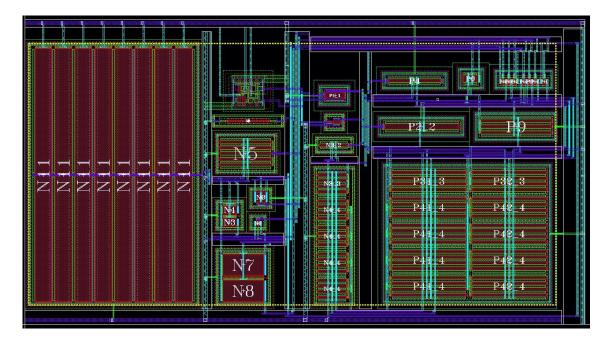

| Figure 39: Final Layout                                              | 62 |

| Figure 40: Starting the program                                      | 63 |

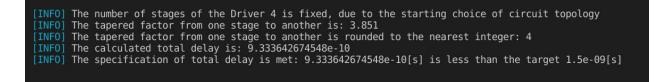

| Figure 42: Requirement check                                         | 65 |

| Figure 43: Asymmetrical sizing option                                | 65 |

| Figure 44: Asymmetrical sizing result                                | 65 |

| Figure 45: Main measurements – typical conditions                    | 68 |

| Figure 46: Main measurements – corner conditions                     | 69 |

| Figure 47: Main measurements – montecarlo conditions                 | 69 |

| Figure 48: Worst case table                                          |    |

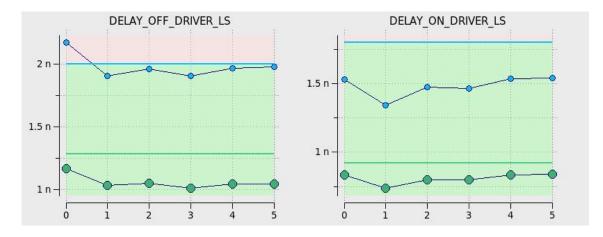

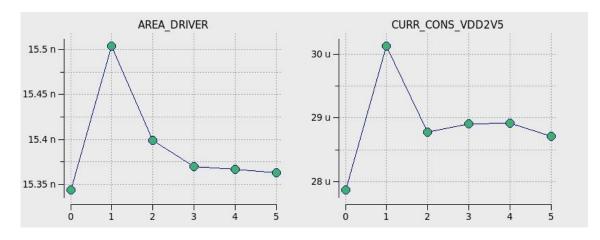

| Figure 49: Delay on and off measures in WiCked                       | 86 |

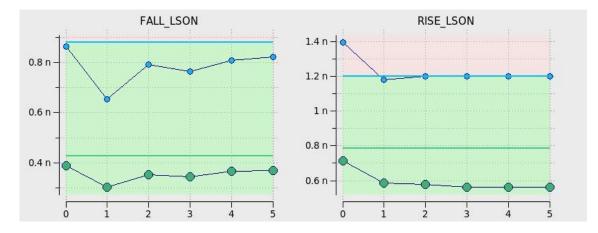

| Figure 50: Fall and rise measures in WiCked                          | 86 |

| Figure 51: Current leakage measure in WiCked                         |    |

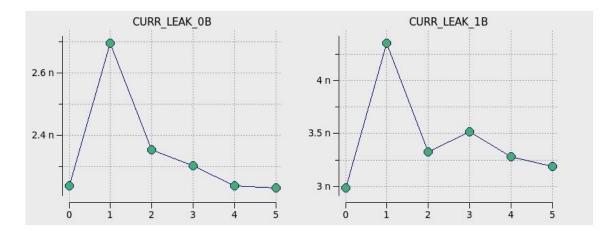

| Figure 52: Area and current dynamic measure in WiCked                |    |

| Figure 53: Legend for the WiCked graphs                              |    |

| Figure 54: WiCked table summary                                      |    |

| Figure 55: Final sizing                                              |    |

| Figure 56: Main measurements with WiCked sizing – typical conditions |    |

| Figure 57: Main measurements with WiCked sizing – corner conditions  |    |

| Figure 58: Main measurements with WiCked sizing – Montecarlo conditions90          |

|------------------------------------------------------------------------------------|

| Figure 59: Final Layoutafter WiCked sizing91                                       |

| Figure 60: Main measurements with WiCked sizing – Typical conditions – Post layout |

| Verification                                                                       |

| Figure 61: Main measurements with WiCked sizing – Corner conditions – Post Layout  |

| Verification                                                                       |

| Figure 62: Main measurements with WiCked sizing – Montecarlo conditions – Post     |

| Layout Verification                                                                |

# Listings

| 1.1 | Commands to start a Qgen project                     | .20  |

|-----|------------------------------------------------------|------|

| 2.1 | List of the devices to be sized                      | .37  |

| 2.2 | Initial condition method                             | .38  |

| 2.3 | Trade off sizing for the driver                      | .40  |

| 2.4 | Asymmetrical sizing method for the driver            | .43  |

| 3.1 | Layout Generator code                                | .55  |

| 4.1 | Verify method to launch Avenue                       | .67  |

| 4.2 | Driver function for optimization                     | .71  |

| 4.3 | Code for user interaction with WiCked                | . 82 |

| 4.4 | Method that sizes the driver according WiCked values | 83   |

# CHAPTER 1 INTRODUCTION

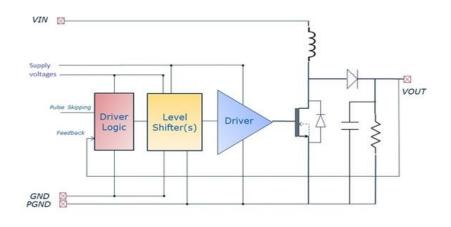

Nowadays the semiconductor industry has to respond to an ever-growing market for integrated circuits (ICs). The creation of increasingly complex chips, as predicted by Moore's law, and the increase in demand in every sector are the main challenges the microelectronics industry has to face. The exponential growth in chip complexity means a complicated and slow design process on the one hand and high costs and long time-to-market on the other.

The main objective for companies is to respond to the growth in demand of quality and efficient products, while keeping low time-to-market and costs.

If we take a detailed look at the chip manufacturing process, one factor that can cause delays is the presence of errors during the design phase, which then leads to delays that inevitably increase the cost of the design. In fact, finding of an error leads not only to the malfunctioning of the chip, but also to redesign and verify all the circuit characteristics, leading to a delayed production beginnings.

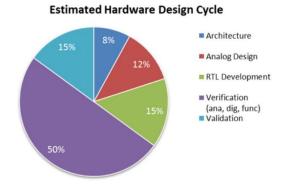

We can better understand the design cycle and the important steps that make it up, by looking at the pie chart below.

Figure 1: Estimated hardware design

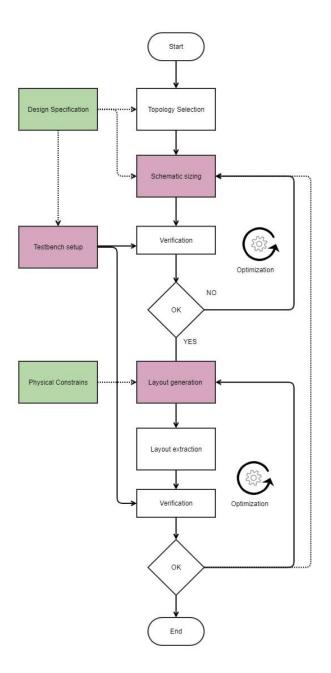

As can be seen in Figure 1, the dominant part of the design cycle is verification, so if it is done carefully, costs and time can be minimised. In this phase all the necessary tests must be performed, involving the worst-case circuit working condition, varying several variables affecting the circuit, taking into account an ageing factor, etc., before the component is manufactured. To better understand why the verification is critical, it is necessary to know what the general workflow for the complete process is:

- Simulate the chosen design under typical conditions to ensure that all the specifications are met.

- Simulate again, but in corner conditions, i.e. varying temperature and voltage/current supplies between their minimum and maximum values, also taking into account process variation.

- Simulate again, but including the statistical distribution for process and devices parameters (mismatch).

- Draw the layout and get a netlist which includes parasitic resistances and capacitances introduced by the layout design.

• Perform point 1 to 3 using the extracted view got at point 4 instead of the schematic view.

In case of fails during one of these steps, a modification of the design is needed and all the verification cycle need to start from the beginning too. Only when all the tests are passed, through potentially a large number of iterations and loops, it is possible to move on to the fabrication phase and it is easy to see that the more complex the circuit, the more time this verification step requires. It is clear that by reducing the time needed for these expensive steps, the total cost of the design cycle will be reduced and a faster process will also get along with the always decreasing time-to-market request.

It must also be emphasised that both a digital and an analogue part can be found in a chip. As seen from the pie-chart, the analogue design is another important slice to consider in the process and also it represents the bottleneck of the design phase and contributes to the slowing down of the design process. Indeed, if for the digital part there are already advanced tools for design automation and verification, the same cannot be said for the analogue part.

The challenge is to develop something similar to what is already existing for the digital part, without forgetting the peculiarity and characteristics of the analog nature.

The use of specific computer-aided design (CAD) methodologies and tools are required to achieve an efficient result; in this sense, reuse-based design practices are regarded as a promising solution.

Therefore, in order to achieve low time-to-market and reduce costs for companies and at the same time automate the design process of analogue parts, like digital ones, automatic design tools and methodologies were adopted at Infineon, guaranteeing top-quality results.

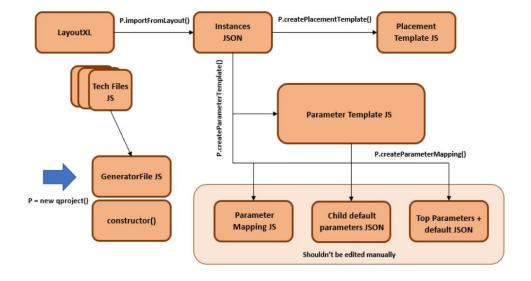

This thesis proposes and develops an approach to schematic and layout design, through the use of framework and tools, such as Anagen, Wicked and H-Qgen. The aim is to move from a traditional method, in which the focus was on the design of individual instances that could not be reused and were created specifically to meet certain specifications, to a design that focuses on the creation of instance generators, called analog generators.

Thanks to these generators, starting from a specific topology it is possible to obtain IP blocks dimensioned according to the specifications provided as input. In the case that the design specifications have to be modified, the re-design takes place very quickly when compared with the time required by the traditional methodology.

It can therefore be stated that analog generators captures the designer methodology and aim to speed up the design process and at the same time to be an assistance tool, capable of providing blocks reliably sized according to the specifications.

Generators must be designed for both schematic and layout, starting with the chosen topology. The following paragraphs present the tools that have enabled the realisation of such a generator.

## **1.1 ANAGEN**

ANAGEN is a hierarchical design framework written in Python: the aim is to automate the design of analogue blocks in analog mixed circuits through the realisation of generators that are independent of process and technology [1].

Started with open source Python framework BAG (Barkley Analog Generator) which is a modular collection of scripts helping in design automation from Berkeley Wireless Research Center, Infineon has decided to develop its own specific flow: ANAGEN. It is more than a framework, it is a collection of tools/APIs to do design automation in an Infineon environment whose objective is to enable users to create, use and test process portable analog generators. The ANAGEN program enables a combined usage of algorithmic design optimization (gm/ID, Wicked), different layout generator engines (Berkeley xBase, Infineon Qgen) together with traditional design, verification flows and tools within the Infineon Camino design flow.

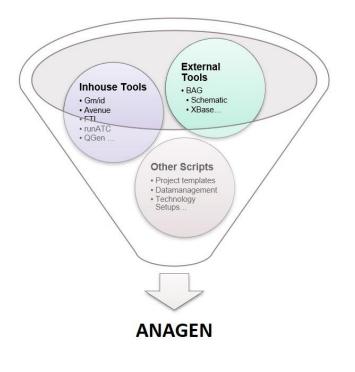

Figure 2: ANAGEN

As can be seen in the Figure 2, the subflow aims at bundling all tools necessary for generator development. The designer can create a template of a schematic and write a script which encapsulates the sizing process for the devices of the circuit, also known as the methodology, in a parametrized way. This creates a win-win situation in that designers and layouters can focus on essential tasks and spend less time on standard tasks, even if custom analog designers have been very resistant to this style of automation. The reasons are different, starting with the resistance to learning coding to the difficulty of analogue design as it changes in each circuit. The main difficulties encountered with this change in design methodology with ANAGEN are as follows:

- The complexity of geometric constraints: Analog layouts require precise matching and symmetry, and layout engineers use clever techniques based on human intuition and expertise. To match this, algorithmic methods must cover a large search space, and this has been infeasible in the past

- The absence of unifying performance metrics: unlike digital designs, which are characterized by power, performance, and area (PPA), the performance specifications of analog circuits are different for each class of circuits

- The wide variety of circuit classes and topologies: there is no equivalent for the relatively compact standard cell libraries used for digital design, and even basic analog building blocks can be constructed in a large variety of ways.

As mentioned earlier, ANAGEN follows a programmatic approach, i.e. it does not deliver instances, but rather captures designer's best approaches in generators, in such a way as to overcome all the difficulties exposed.

The generators focus on schematic, layout and verification, implementing the concept of reusability combined with automation. Productivity gains come from parametrization, incremental extension and process portability. With all these features, the impact of ANAGEN in the design process is more than positive, speeding up key steps.

Through the creation of a reference library of designs, with a simple selection of the concept concerned and readjustment to the new work, a great deal of time is saved, as well as costs; however, everything must be well organised and well documented.

As it is easy to understand, the design methodology allows for the preservation of the modus operandi, rather than a specific product.

Finally, optimisation algorithms, obtained through a mix of the field of expertise and knowledgebased optimisation methods, can solve complex but definite problems. ANAGEN is written in Python using the object-oriented programming (OOP) model, organizing the software design around data or objects, instead of functions and logic. This approach also reflects the concept of reuse, since it embeds a hierarchical structure, making the reuse of the code itself easier through objects with relationship like parent-child.

ANAGEN provides in details:

- ANAGEN server, which contains already created generators that can be installed from Cadence-Virtuoso directly.

- ANAGEN technology setups, which allow the definition of a device flavor<sup>1</sup>

- Python API<sup>2</sup>, which is very powerful and user-friendly, and also provides lots of functional packages and classes for the generators

- Python Wrapper, which makes it possible to run simulations in Cadence-Virtuoso

- Example Generators: There are many open-source templates and examples

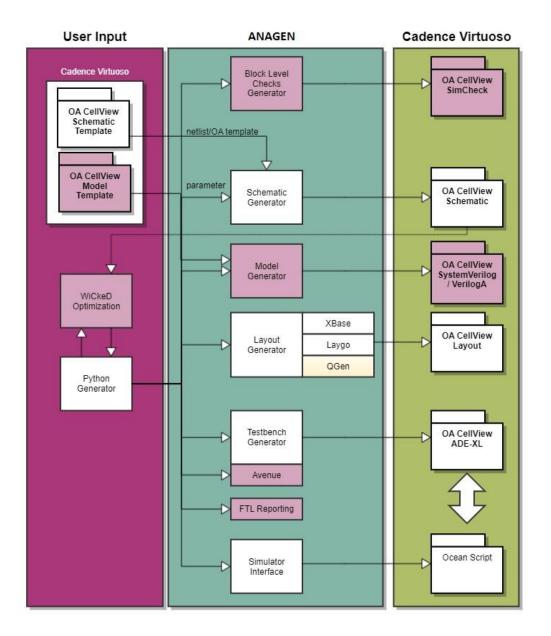

The framework structure can be seen in the Figure 3.

Figure 3: Anagen Framework

The starting point to create a generator is the topology of the circuit, which will not be alterated or manipulated, but it remains fixed.

As already mentioned, this framework provides the implementation of various functions such as dimensioning, schematic implementation, layout and verification: as can be seen from Figure 1.3, the Python generator, which is the actual user input, provides the various instance generators together with the verifications, which in turn communicate with the Cadence design environment, i.e. Virtuoso. Generator are written in Python and these scripts communicate directly with the users Virtuoso instance, thanks to low-level ANAGEN libraries via SKILL commands, while the generated instances are available immediately in Cadence-Virtuoso for debugging and tuning.

In the ANAGEN version, the blocks highlighted in pink in Figure1.3 constitute the upgrades made from the previous version. Of particular interest is the Wicked optimization block, which makes it possible to optimize the schematic implemented by the generator (more details in the next paragraph).

A simplified version of the framework structure is presented in Figure 4.

Figure 4: ANAGEN Framework simplified

As can be seen in this simplified version of anagen illustrated in Figure 1.4, the main blocks of the framework are those who permit the coding of generators, specifically: schematic generator, layout generator and testbench generator.

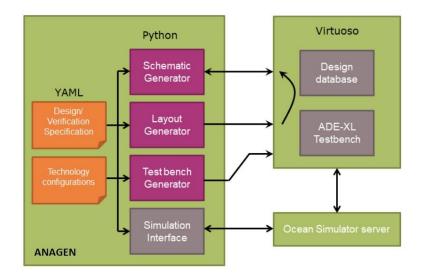

Therefore ANAGEN provides all the tools needed to develop a generator of a circuit topology specified as input. However, attention must be paid to the flow to be followed to create a generator. The complete flow is presented in Figure 5.

Figure 5: Anagen Workflow

It is important to visualize the flow that has to be followed in order to produce a reliable generator, while noticing that verification and optimization can also be included in the schematic generator itself. If something is not good enough at the schematic verification then it is not possible to proceed with the layout and an optimization step is needed to achieve a performing circuit.

The flow embeds the design approach to be adopted at programming level, which consists on four important parts. The initial setup phase in which:

- Create a template of the intended circuit

- Parametrize properties (transistor length and width, capacitors and resistors size)

- Create a verification setup

Then it proceeds with the second phase of initial sizing:

- Translate the system requirements into circuit requirements

- Perform initial sizing with the gm/ID methodology or other suited methogology, implementing the schematic generator

After that, the third phase regards the optimiser:

- Define optimization objectives and constraints

- Run the optimizer on the constrained sizing problem

- Typical run times are in the order of minutes / few hours

After the phase concerning the design and optimisation of the schematic is finished, the last phase proceeds with the layout:

- Execute a layout generator

- Run design rule check and perform parasitic extraction

• Run final verification, and IP release

If problems are found in the verification phase, the layout phase is repeated, otherwise the optimisation with the initially identified constraints is carried out also for the final part.

So as one can guess this process is iterative, each time a specification is not met, the flow has to go back to the schematic or layout generator and change some parameters according to the script, as a designer would do by hand. Once the topology has been selected and the relative schematic has been produced with devices belonging to ANAGEN, therefore of possible manipulation through Python code, it is possible to start a project with a Python template inside the integrated development environment IDE. This file.py contains the class generator in which all the coding strategy for the sizing of the schematic is written. Instead, for the coding of the layout generator, it is necessary to refer to other javascript language files. For this thesis only the schematic sizing has involved the use of ANAGEN, while the tool that has been used for the layout is Qgen, which currently is independent of ANAGEN. So to summarise, the main objective remains the development of generators that deliver quality results and reduce time-to-market. This can partially be achieved through the coding of a methodology based on the experience and knowledge of the designer, and also through optimization algorithms, either coded at the moment or imported from existing optimization tools (e.g. MunEDA WiCked, pymoo etc.).

### 1.2 WiCked

WiCked is a tool that is part of a larger group of EDA solutions provided by the software company MunEDA [2]. This is a software suite that adds more functionalities to existing EDA design environments. The acronym EDA stands for *Electronic Design Automation* and can be defined as the category of tools used for designing and manufacturing electronic systems, from printed circuit boards to integrated circuits. The tool can be used for different purposes, for instance the analysis and optimisation of the yield and performance of analogue, mixed-signal and digital designs [3].

MunEDAs tools provide different skills for IP porting, re-sizing, re-targeting, analysis and verification, modelling and even sizing and optimization for full-custom design in advanced technologies.

WiCkeD helps the circuit designer to improve the efficiency, decrease the risk of failures and increase the circuit quality, through the consideration of statistical variation effects of modern process technologies.

Several tools and features of this environment are made available.

Here is a list of them:

- FEO *Feasibility Analysis and Optimization* Defines and analyses the circuit's functionality based on the electrical, layout, area and others constraints running automatically netlist parametrization and optimizes and fulfills them automatically for best functionality

- DNO *Deterministic Nominal Optimization* Sensitivity based circuit optimization for nominal (typical) case and worst case operating corners

- GNO *Global Nominal Optimization* Statistical and stochastic circuit optimization based on sampling and design-space exploration search algorithms

- YOP *Yield Optimization* Automated circuit yield and robustness optimization for high sigma and performance margins

- REL *Reliability Option* includes and considers available reliability models and constraints for enhanced aging, degradation, area and other reliability influence factors

The tool can be configured and executed in script-based (batch mode) or fully GUIdriven. Optimization is based on complete specifications and constraints are managed by the tool itself, trying to satisfy all of them. It is proven in wide range of technologies from 350nm CMOS down to 5nm FinFET advanced node PDK.

We can make a list of benefits which ranges from automatic performance tuning for all types of analogue and mixed-signal circuits (amplifiers, transceivers, PLLs, oscillators, mixers, data converters, filters and many more) to optimisation of performance, robustness and highsigma.

Consequently we can mark improvements in different fields such as performance, power, area, delay, as well as parasitic effects and design time effort.

Since March 2021, WiCked has been used productively as a mathematical plug-in of Infineon IP Factory to statistically characterise standard cell. The challenge is to achieve a high accuracy by using various machine learning techniques, such as worst-case analysis, interpolation, adaptive determination of interpolation points and many more. In order to reduce the overall execution time, parallel processing and simulations are used.

Figure 6 shows the tasks that the optimizer is able to provide; for this thesis, circuit optimisation at PVT corners is of interest.

| Monte Carlo, PVT and High-Sigma Variation   | n Analysis         |

|---------------------------------------------|--------------------|

| Circuit Optimization at PVT Corners         |                    |

| Circuit Optimization including MC variation | PVT and High-Sigma |

| Load State                                  |                    |

Figure 6: WiCked Tasks

After selecting the task of interest, if the session is started in batch mode, the netlist for the project of interest is selected manually, otherwise it will be selected automatically. In the constraint editor window, one can set the optimiser according to interest case and parameterise the parameters of interest and set acceptable ranges for them, set pvt corners (process, voltage, temperature) combining them with acceptable temperature and power ranges. Finally, in the section performance there are all the measurements to be made with the type of analysis (dc, tran...) as well as the possibility of adding area measurement.

| File Options I          | 100 <sup>-7</sup>                                                                           | WiCkeD Constr    | aint Editor 8.0-1 (Desig                                                        | n:tb_e | lriver.rs) <1>                   |        |                 | ^ _ D             |

|-------------------------|---------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------|--------|----------------------------------|--------|-----------------|-------------------|

| Setup                   | Matched Devices Parameterice Properties                                                     |                  |                                                                                 |        |                                  |        |                 |                   |

| 1000                    | ksterces Properties                                                                         |                  |                                                                                 |        |                                  |        |                 |                   |

|                         | Instance                                                                                    | Properties Model |                                                                                 | Prop   | arty                             |        |                 | Parameter / Value |

| Parameterize            | A_CEANEX<br>A_CEACEIP,X                                                                     |                  | 10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>1 |        |                                  |        |                 |                   |

| 121                     | <ul> <li>A_CERUF2.X</li> <li>A_CERUF3.X</li> </ul>                                          |                  | 9                                                                               |        |                                  |        |                 |                   |

| Corners &               | A_CSIVI,X<br>A_CSIVI,X                                                                      |                  | B                                                                               |        |                                  |        |                 |                   |

| Operating<br>Parameters | A_CSLNDZ,K                                                                                  |                  |                                                                                 |        |                                  |        |                 |                   |

| <u>.</u>                | A_CSLNRZ,X<br>A_CSLNRZ,X                                                                    |                  |                                                                                 |        |                                  |        |                 |                   |

| Constraints             | <ul> <li>A_CSTEONEX</li> <li>A_CSTEZERO,X</li> </ul>                                        |                  |                                                                                 |        |                                  |        |                 |                   |

| -                       | DOOST_DRIVER_LS,X<br>BOOST_DRIVER_LS_LVLSH(X)                                               |                  |                                                                                 |        |                                  |        |                 |                   |

| Performances            | <ul> <li>BOOST_DRIVER_LS_TAPERED_BUFFER.X</li> <li>BOOST_LVSHIT_STATIC_TV5_2V5.X</li> </ul> |                  |                                                                                 |        |                                  |        |                 |                   |

|                         | BOOST_MULLS_GTS_CONFIG.X<br>BOOST_SWHS_X                                                    |                  |                                                                                 |        |                                  |        |                 |                   |

|                         | BOOST_SWLS_X<br>ESD_TVS_GP96,N                                                              |                  |                                                                                 |        |                                  |        |                 |                   |

|                         | H150_SAN2.X                                                                                 |                  |                                                                                 |        | Parameters                       |        |                 |                   |

|                         | <ul> <li>H150_580F3.X</li> <li>H150_58V1.X</li> </ul>                                       |                  |                                                                                 | Use    |                                  |        | Upper Intervals |                   |

|                         | HISE SAREX                                                                                  |                  |                                                                                 |        | EN_FULLPW<br>EN_PD               | 0      |                 |                   |

|                         | H150LL_SBUFICK                                                                              |                  |                                                                                 |        | FREQ                             | 440000 |                 |                   |

|                         | H180L_SBUF2,X                                                                               |                  |                                                                                 |        | TEMPERATURE (Global temperature) | 27     |                 |                   |

|                         | H150LL_SIV1,X                                                                               |                  |                                                                                 |        | TM_SEL0                          | 0      |                 |                   |

|                         | ▶ HIDRL_SIVEX                                                                               |                  |                                                                                 |        | TM_SEL1                          | 0      |                 |                   |

|                         | H150LL_BORZ,R                                                                               |                  |                                                                                 |        | VD01V5                           | 1.5    |                 |                   |

|                         | ➡ Topever of testienches                                                                    |                  |                                                                                 |        | VDD2V5                           | 2.5    |                 |                   |

|                         | Ap_driversi                                                                                 |                  |                                                                                 |        | VDDSV                            | 5      |                 |                   |

|                         |                                                                                             |                  |                                                                                 |        | VSTATIC                          | 0      |                 |                   |

|                         |                                                                                             |                  |                                                                                 |        | XTRCT                            | 0      |                 |                   |

|                         |                                                                                             |                  |                                                                                 |        |                                  |        |                 |                   |

|                         |                                                                                             |                  |                                                                                 |        |                                  |        |                 |                   |

| ٢                       |                                                                                             |                  |                                                                                 |        |                                  |        |                 |                   |

| Start WICkeD            | Modified                                                                                    |                  |                                                                                 |        |                                  |        |                 |                   |

| Status: Ready           |                                                                                             |                  |                                                                                 |        |                                  |        |                 | 1                 |

Figure 7: Constraint Editor

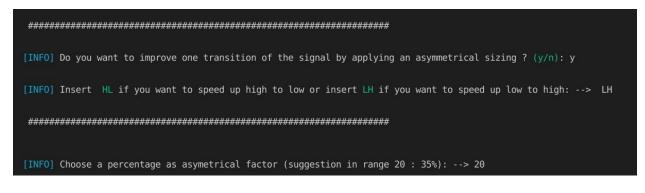

After setting up the optimiser, it can be launched. This opens the WiCked GUI as in Figure 8, where the tools of interest can be used. For the thesis, three tools are used:

- 1. Simulation: in which a nominal simulation of the circuit is made and it is checked whether the results obtained are those expected

- 2. Worst-case Operation & Corner: the circuit is simulated in such a way as to identify which combination of corners (temperature, power supply, process...) leads the circuit to the worst behaviour, in this way it can be seen how performance degrades as the conditions of interest change

- 3. DNO Deterministic Nominal Optimisation the actual optimisation is carried out, after setting performance bounds or specifying a minimisation; the tool varies the parameters that were set in the previous phase and provides suitable values to be inserted into the circuit for it to behave in the optimum way.

| <u>*</u>                               | WiCkeD 8.0-1 (Design: tb_driver.rs) - Simulation (Ne                      | ode 1) <1>                   | ^ _ D >     |

|----------------------------------------|---------------------------------------------------------------------------|------------------------------|-------------|

| File Analysis Options Help             |                                                                           |                              |             |

| lesign History                         |                                                                           |                              |             |

| 0                                      | Parameters                                                                | Results                      |             |

|                                        |                                                                           | Performances                 |             |

|                                        |                                                                           | Manne                        | Value       |

|                                        |                                                                           | CURR_LEAK_08<br>CURR_LEAK_18 |             |

|                                        |                                                                           | CURR_CONS_VDD2V5             |             |

|                                        |                                                                           | CURR_CONS_VDD1V5             |             |

|                                        |                                                                           | RISE_LSON<br>FALL_LSON       |             |

|                                        |                                                                           | DELAY_ON_DRIVER_LS           |             |

|                                        |                                                                           | DELAY_OFF_DRIVER_LS          |             |

|                                        |                                                                           |                              |             |

|                                        |                                                                           | 1                            |             |

|                                        |                                                                           |                              |             |

|                                        |                                                                           |                              |             |

|                                        |                                                                           |                              |             |

|                                        |                                                                           |                              |             |

|                                        |                                                                           |                              |             |

| Tools                                  |                                                                           |                              |             |

| 100 Simulation                         |                                                                           |                              |             |

| / Sensitivity Analysis                 |                                                                           |                              |             |

| Screening                              |                                                                           |                              |             |

|                                        |                                                                           |                              |             |

|                                        | Simulation Environment Main Log                                           |                              | ++-         |

| Gerministic Feasibility Optimization   | Created by : WiCkeD 8.U-1<br>Date : 08/29/2022                            |                              | • •         |

| Global Feasibility Optimization        | Time : 09:45:01<br>Hostname : vihici393 with IF address 10.162.1.188      |                              | Q           |

| (a) Deterministic Nominal Optimization | Operating System : Linux (4.18.0-305.34.2.e18 4.x86_64)                   |                              | 4<br>0<br>> |

| Global Nominal Optimization            | Machine : x86_64<br>User : demirid                                        |                              | P           |

| W Notepad                              | Log Level : Normal                                                        |                              |             |

|                                        | <pre></pre>                                                               |                              |             |

|                                        | <09:45:00> Cannot start license manager communication for package license |                              |             |

|                                        | <09:45:00> No such file or directory                                      | 5                            |             |

|                                        | <09:45:10> Appended Simulation (#1) to Root node.                         |                              |             |

Figure 8: WiCked GUI

For this thesis the optimiser has been used, but not included in the 'automatic' flow as this phase is still in the development phase. The results obtained using WiCked will however be presented in the following chapters.

### 1.3 Qgen

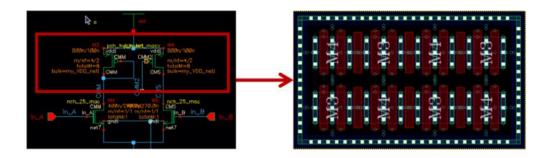

Infineon Technologies has developed an in-house layout module generator, called Qgen. This tool is written in C++ using the  $Qt^1$  framework, whereas technologies setups and generators, called from C++ interface, are written in JavaScript.

A first problem regards the integration of the use of JavaScript in the flow, since the ANAGEN framework is written in Python, and therefore schematic generator and the layout generator cannot be put in a complete automatic design loop.

Qgen is the chosen tool for this thesis work because it is able to deal with the used technology and also for different reasons [4]:

- Reduce layout implementation time compared to the one made by hand.

- Fast exploration of instance and layout parameters.

- Qgen instances are OA figGroups (instances of PDK PCells<sup>2</sup>, Vias, shapes)

- Formally correct (e.g. no undesired shorts created).

- Layout XL compliant.

<sup>1</sup> Qt is a widget toolkit for creating graphical user interfaces as well as cross-platform applications <sup>2</sup> A PCell is a parametrized cell which represents a part or a component of the circuit whose structure is dependent on one or more parameters

Figure 9: Qgen transistor matrix

|                                   | transistar_matrix parameters (on whi        | (1252) • • •      |                                                                        | transistor_matrix parame       |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------|---------------------------------------------|-------------------|------------------------------------------------------------------------|--------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| esign Dummy Guardining Ga         | ate Houting DramSource Houting Herarchica + | Placement Layout  | Design Dummy Guarding Gate                                             | Routing DramSource Routing Her | athici * Platement | Tanks 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| edel.                             | simpla -                                    |                   | Drain/Source mulling                                                   | Route Over Device              | -                  | Cablor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| stances                           | P1 P2                                       |                   | Dramfour(e routing track over gate track                               | <ul> <li>C</li> </ul>          |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Show shetails                     | Width 60 60                                 |                   | Optimize reading track over device                                     |                                |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Attional instance parameters      |                                             |                   | Drain source routing layer                                             | route#2                        | -                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Assets:                           |                                             |                   | Stack drain source routing layer up to                                 | Pione                          | · .                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| it length:                        | 1,200 um                                    |                   | Route D/S of device vertically<br>Route D/S of dummy device vertically |                                |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| reper of feature                  | 1.                                          |                   | Dran source with                                                       | 0.000 um                       |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| t with                            | 10.000 um                                   | P1 P2 P1 P2 P1 P2 |                                                                        | B 600 um                       |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A well's<br>C - Wall proximity    | to out and                                  | P1 P2 P1 P2 P1 P2 | Spread dran source<br>Extend D/S routing over dammy devices            | a 000 um                       |                    | 21-192-191-192-191-192                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

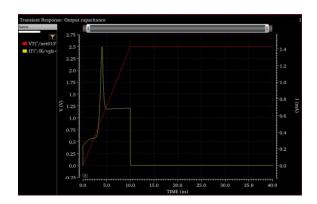

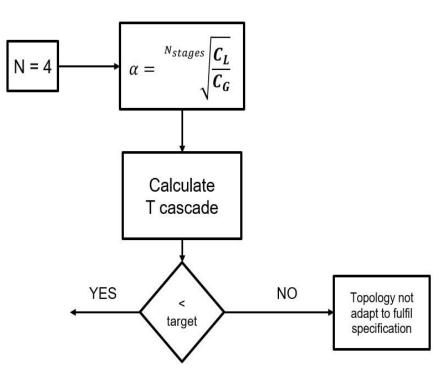

| E - STI Horizontal OD spacing     | 0.000 um                                    |                   | Cover D/S tracks with guard rings                                      |                                |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |